## **Learning Objectives**

After completing this chapter, you will learn the following:

- Broad classification of oscillators based on the type of output waveform.

- Different constituents of an oscillator circuit.

- Barkhausen criterion of oscillations including gain and phase shift conditions.

- Different types of oscillator circuits.

- RC oscillators including RC phase shift, Wien bridge, Quadrature, Twin-T and Bubba oscillators.

- LC oscillators including Hartley, Colpitt and Clapp oscillators.

- Crystal oscillators including Pierce oscillator.

- Voltage-controlled oscillators.

- Frequency stability considerations.

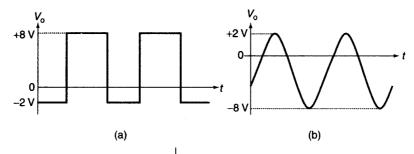

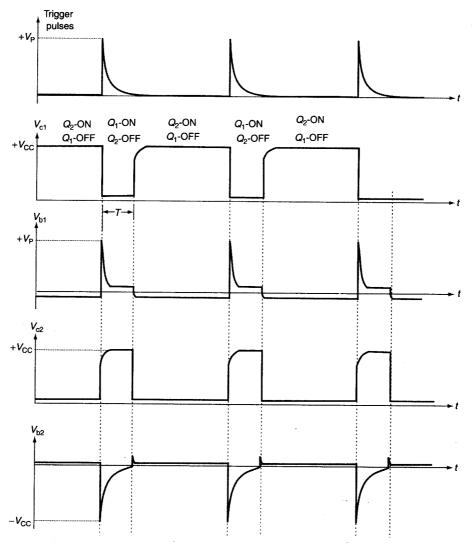

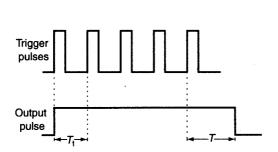

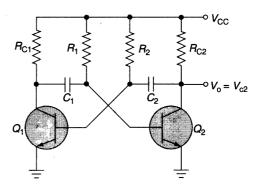

Discussion on amplifiers is almost invariably followed by the one on oscillators. There are two broad categories of oscillators, namely, the sinusoidal and the non-sinusoidal oscillators. Sinusoidal oscillators discussed in this chapter generate sine wave output. Important types in the non-sinusoidal category are the ones that generate square wave or pulsed outputs. A multivibrator is type of non-sinusoidal oscillator. Multivibrator circuits are discussed in Chapter 13 on wave-shaping circuits. An amplifier is in fact the central building block of an oscillator. While the former has a negative feedback to have increased stability and reduced distortion, the latter is an amplifier with a positive feedback. Major topics discussed in this chapter include oscillator fundamentals like the Barkhausen criterion for oscillations, popular oscillator circuit configurations, which include different types of RC, LC and crystal oscillators and oscillator frequency stability considerations.

## 12.1 Classification of Oscillators

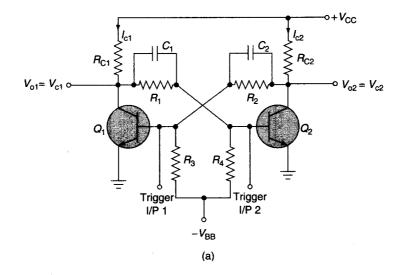

On the basis of the type of output waveform generated, oscillators are classified as sinusoidal and non-sinusoidal oscillators. Sinusoidal oscillators produce a sine wave output where as non-sinusoidal oscillators produce square or pulsed output. A multivibrator circuit is a type of non-sinusoidal oscillator. Different types of multivibrator circuits are discussed in detail in Chapter 13 on wave-shaping circuits for reasons that would be obvious as we go through the operational basics of the two types of oscillators circuits

in respective chapters. The only thing common between the two types of oscillator circuits is that both types have an inherent regenerative feedback.

Depending upon the nature of the feedback network used, sinusoidal oscillators are further classified as RC, LC and crystal oscillators.

## 12.2 Conditions for Oscillations: Barkhausen Criterion

An oscillator circuit is essentially an amplifier circuit with a frequency-selective feedback network. The feedback network feeds a fraction of the amplifier output back to its input in such a way as to satisfy the two fundamental requirements for occurrence of sustained oscillations. These requirements are commonly known by the name of *Barkhausen criterion*.

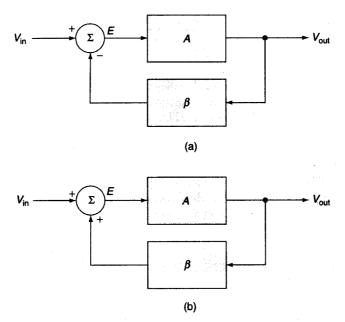

Barkhausen criterion can be best explained by considering the canonical form of negative and positive feedback systems as shown in Figures 12.1(a) and (b), respectively. Canonical form is the simplest form of representation of any class of systems without any loss of generality. The transfer function in the case of negative feedback system of Figure 12.1(a) can be derived as follows. Remember that in the case of a negative feedback system, the summing point is a subtractor. That is, the error signal is the sum of input signal and the phase-inverted feedback signal:

$$E = V_{\rm in} - \beta \times V_{\rm out} \tag{12.1}$$

Substituting  $E = V_{\text{out}}/A$ , we get

$$\frac{V_{\text{out}}}{A} = V_{\text{in}} - \beta \times V_{\text{out}}$$

(12.2)

Figure 12.1 Canonical form of feedback systems: (a) Negative feedback system; (b) positive feedback system.

This simplifies to

$$\frac{V_{\text{out}}}{V} = \frac{A}{1 + \beta A} \tag{12.3}$$

In the case of a positive feedback system in which the summing point is an adder, the transfer function is given by

$$\frac{V_{\text{out}}}{V_{\text{in}}} = \frac{A}{1 - \beta A} \tag{12.4}$$

If  $\beta A = -1 = 1 \angle -180^\circ$  in the case of negative feedback system and  $\beta A = 1 = 1 \angle 0^\circ$  in the case of positive feedback system, the system works like an oscillator. In the case of the former, the conditions specify magnitude of loop gain as unity and loop phase shift as 180°. In the case of latter, the conditions specify magnitude of loop gain as unity and loop phase shift as 0° or 360°. The condition for the magnitude of the loop gain is the same in the two cases. If we carefully examine the two cases, we will find that the loop phase shift condition in both the cases is also the same as phase inversion implied by the negative sign at the summing point of the negative feedback system restores the overall phase shift at the amplifier input. Essentially the two conditions mean the following:

- 1. The magnitude of loop gain is unity, which ensures that the feedback signal has the same magnitude as that of the input signal.

- 2. The magnitude of loop phase shift is such that the feedback signal is in-phase with the input signal when it reaches the input of the amplifier.

These two conditions define what is known as Barkhausen criterion of oscillations. Satisfying Barkhausen criterion ensures that oscillator circuits do not need an external applied input signal. Instead they use fraction of the output signal as the input signal.

In practical oscillator circuits, the summing point is an adder and therefore the Barkhausen criterion of oscillations is written as follows:

- 1.  $|\beta A| = 1$ . That is, loop gain should be unity.

- 2.  $\angle \beta A = 0^{\circ}$  or integral multiple of 360°. That is, loop phase shift should be zero or integral multiple of 360°.

### **Initiation of Oscillations**

The process of generation of oscillations is initiated due to some inevitable noise present at the amplifier input. The amplified output due to noise has all frequency components. Since the feedback network is a frequency selective one and the loop phase shift condition is satisfied only at one frequency, the signal fed back to the input has a single frequency component at which the loop phase shift condition of the Barkhausen criterion is satisfied. This leads to the oscillator circuit producing a sinusoidal output.

The essential condition for the magnitude of loop gain for oscillations to occur is that loop gain is precisely unity. There is every possibility that with change in parameters of the transistor or other active devices used in the amplifier part of the oscillator due to ageing or replacement, one lands up with loop gain less than unity. In that case there will be no oscillations. So, in practice, loop gain is kept slightly greater than unity to ensure that oscillator works even if there is a slight change in the circuit parameters. Moreover, there is no harm in keeping loop gain slightly greater than unity as the output cannot increase infinitely as it appears because the output amplitude will be limited due to onset of non-linearity of the active device used. However, if magnitude of loop gain is much larger than unity, the oscillator output will have lot of distortion.

# 12.3 Types of Oscillators

Sinusoidal oscillators are classified on the basis of the type of frequency-selective network used in the feedback loop. Different types include the following.

- 1. RC oscillators;

- 2. LC oscillators;

- 3. Crystal oscillators.

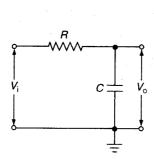

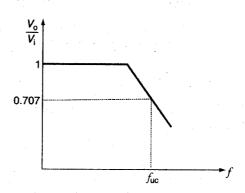

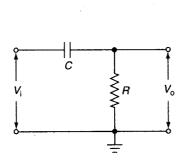

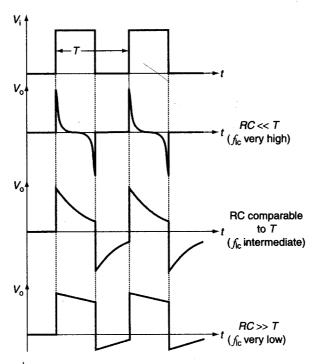

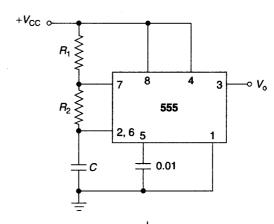

#### RC Oscillators

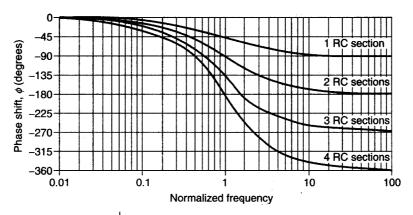

In the case of RC oscillators, multiple RC sections are used to provide the required phase shift. Remember that a single section RC or RL network provides up to a maximum of 90° of phase shift due to existence of a single pole in its transfer function. A minimum of two sections would therefore be required to provide the required  $180^{\circ}$  of phase shift. In practice, cascade arrangement of three RC sections is used in practical RC phase shift oscillators with each section providing  $60^{\circ}$  of phase shift. This provides a larger value of rate of change of phase with frequency around the operational frequency  $(d\phi/d\omega)$ , which gives improved performance in terms of frequency stability. Frequency stability issues are discussed in detail in the latter part of the chapter. Figure 12.2 shows the plot of phase as a function of frequency in the case of multiple RC sections.

Prominent candidates in the category of RC oscillators include the RC phase shift oscillator, Twin-T oscillator, Wien bridge oscillator, Bubba oscillator and Quadrature oscillator.

#### LC Oscillators

A single-section LC circuit has two poles and therefore can provide the required 180° of phase shift. Prominent members include Hartley oscillator, Colpitt oscillator and Clapp oscillator. LC oscillators are suitable for relatively higher operational frequencies due to low-frequency inductors being expensive, bulky and highly non-ideal. RC oscillators are preferred at lower frequencies.

## Crystal Oscillators

In crystal oscillators, crystal resonator provides the electrical equivalent of frequency-selective network. Crystal oscillators are the most stable of the three types due to their extremely high rate of change of phase with frequency at the operating frequency  $(d\phi/d\omega)$ . Crystal oscillators are not practical at lower operating frequencies due to their size, weight and cost restrictions.

Figure 12.2 | Phase versus frequency plot of RC sections.

Oscillators belonging to each one of the three above-mentioned categories are described in the following sections.

#### **EXAMPLE 12.1**

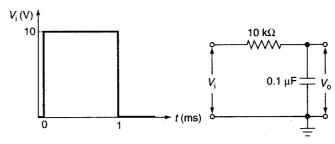

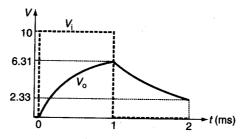

Determine the gain or phase shift as the case may be for the following oscillator circuits.

Case 1: If the feedback network of a certain oscillator provides 1% positive feedback, what should be the minimum gain for the amplifier section of the oscillator for sustained oscillations?

Case 2: If in an oscillator, the amplifier portion is a two-stage CE configuration, what should be the phase shift to be introduced by the feedback network at the oscillation frequency for sustained oscillations?

Case 3: The amplifier gain in an oscillator is 50. What should be the percentage feedback for sustained oscillations?

#### Solution

#### Case 1

- 1. A feedback of 1% means  $\beta = 0.01$ .

- 2. Therefore, amplifier's minimum gain is  $1/\beta = 100$ .

#### Case 2

- 1. A two-stage CE amplifier provides a phase shift of  $2\pi$  radians.

- 2. Therefore, the feedback network must not introduce any more phase shift or introduce phase shift equal to multiples of  $2\pi$  radians in order to satisfy Barkhausen criterion for sustained oscillations.

#### Case 3

- 1. Amplifier gain = 50.

- **2.** Therefore, feedback factor  $\beta = 1/50 = 0.02$ .

- 3. Percentage feedback = 2%.

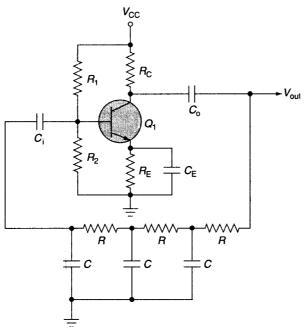

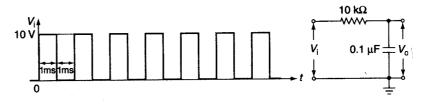

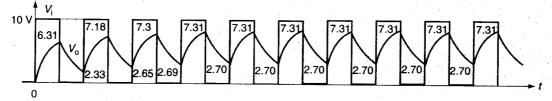

# 12.4 RC Phase Shift Oscillator

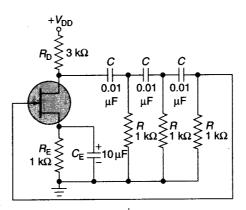

The basic RC phase shift oscillator comprises a single-stage amplifier whose output is fed back to its input through a feedback network. The amplifier portion is usually implemented by either a bipolar junction transistor-based common-emitter amplifier stage or an operational amplifier wired as an inverting amplifier. The feedback network comprises a cascade arrangement of three identical sections of either lag- or lead-type RC network. Figure 12.3 shows the circuit schematic of an RC phase shift oscillator using a common-emitter amplifier stage and a lag-type RC feedback network. This circuit could have been as well implemented using a junction FET-based common-source amplifier stage in place of bipolar junction transistor-based common-emitter stage.

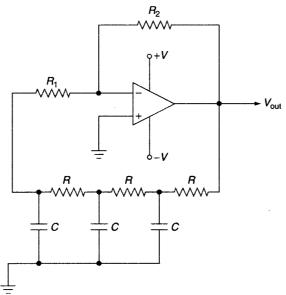

Figure 12.4 shows another version of RC phase shift oscillator in which the amplifier portion is implemented using an operational amplifier configured as an inverting amplifier. In both cases, the amplifier provides a phase shift of 180° at the frequency of operation, which means that the feedback network must also provide an additional phase shift of 180° at the operating frequency to satisfy the loop phase shift condition of the Barkhausen criterion. Also the gain to be provided by the amplifier stage must be at least equal to the inverse of the attenuation factor of the feedback network. In fact, in the phase shift oscillator, while the amplifier gain is dictated by the feedback network attenuation factor; the phase shift provided by the amplifier stage decides the phase shift to be provided by the feedback network.

Figure 12.3 RC phase shift oscillator with lag-type feedback network using common-emitter amplifier.

Figure 12.4 RC phase shift oscillator with lag-type feedback network using operational amplifier.

In order to analyze the oscillator circuits of Figures 12.3 and 12.4, we need to analyze the transfer function of the feedback network. The transfer function will tell us about both the attenuation and the phase shift provided by this network as a function of frequency.

The transfer function of a single-stage lag-type RC network is give by

$$T(s) = \frac{1}{1 + RCs} \tag{12.5}$$

where  $s = j\omega$ .

Assuming that the RC sections in the cascade arrangement are independent of each other, that is, individual RC sections do not load each other, then the transfer function of the cascade arrangement of three RC sections is given by

$$T(s) = \left[\frac{1}{1 + RCs}\right]^3 \tag{12.6}$$

Now, the single-section RC network provides a phase shift  $(\theta)$  given by

$$\theta = \tan^{-1}(-\omega RC) \tag{12.7}$$

$\tan\theta = -\omega RC$

$$\omega = -\frac{\tan \theta}{RC} \tag{12.8}$$

If this single RC section were to provide the desired lagging phase shift of 60° so as to produce a total lagging phase shift of 180° from the feedback network, then the operational frequency of the oscillator would be given by

$$\omega = \frac{-\tan(-60^{\circ})}{RC} = \frac{\sqrt{3}}{RC}, \text{ which gives } f = \frac{\sqrt{3}}{2\pi RC}$$

(12.9)

Attenuation factor provided by single-section RC network is given by

Attenuation factor (single-section RC network) =

$$\frac{1}{\sqrt{1+\omega^2 R^2 C^2}}$$

(12.10)

Substituting the value of  $(\omega)$  from Eq. (12.9), we get

Attenuation factor =

$$1/\sqrt{(1+3)} = 1/2$$

The overall attenuation factor  $(\beta)$  of the feedback network is then given by

$$\beta = (1/2)^3 = 1/8 \tag{12.11}$$

Equation (12.11) implies that the amplifier gain must at least be equal to 8. In practice, it is observed that the required gain is much higher than 8 and also that the oscillation frequency is also higher than that computed by using Eq. (12.9). This is due to the loading effect of different RC sections when they are in cascade arrangement. This is explained in the following paragraphs.

Without going into the mathematics of network analysis, considering the loading effect, it can be proved that the transfer function of the three-section RC network of the lag type is given by

$$T(s) = \frac{(1/RC)^3}{s^3 + (5/RC)s^2 + (6/R^2C^2)s + (1/R^3C^3)}$$

(12.12)

Substituting  $s = j\omega$ , we get

$$T(j\omega) = \frac{(1/RC)^3}{[(1/R^3C^3) - (5\omega^2/RC)] + j[(6\omega/R^2C^2) - \omega^3]}$$

Multiplying both numerator and denominator by  $R^3C^3$ , we get

$$T(j\omega) = \frac{1}{(1 - 5\omega^2 R^2 C^2) + j(6\omega RC - \omega^3 R^3 C^3)}$$

(12.13)

If the feedback network were to provide an overall phase shift of 180°, then the imaginary part should be equal to zero. That is,  $6\omega RC - \omega^3 R^3 C^3 = 0$ , which gives

$$\omega = \sqrt{6} / RC \tag{12.14}$$

Substituting the value of  $\omega$  in Eq. (12.13), we get the expression for the feedback factor as

Feedback factor,

$$\beta = 1/(1-30)$$

(12.15)

This gives

$$|\boldsymbol{\beta}| = 1/29 \tag{12.16}$$

Equations (12.14) and (12.16) specify the required conditions for loop phase shift and loop gain. The oscillation frequency is given by Eq. (12.14) and Eq. (12.16) tells that the amplifier gain must at least be equal to 29.

A similar analysis can be done in the case of lead-type RC phase shift network too. The expressions for the transfer function and the phase shift provided by single-section lead network are given by Eqs. (12.17) and (12.18), respectively.

$$T(s) = \frac{RCs}{1 + RCs} \tag{12.17}$$

$$\theta = \tan^{-1}(1/\omega RC)$$

which gives  $\omega = 1/\sqrt{3}RC$  for  $\theta = 60^{\circ}$ .

(12.18)

Considering the loading effect, the transfer function for the cascade arrangement of three-section lead-type RC network is given by Eq. (12.19). This equation is similar to Eq. (12.13) written for the cascade arrangement of lag network.

$$T(j\omega) = \frac{1}{\{1 - 5/(\omega^2 R^2 C^2)\} - j\{6/(\omega RC) - 1/(R^3 C^3 \omega^3)\}}$$

(12.19)

Again, if the feedback network were to provide an overall phase shift of 180°, then the imaginary part should be equal to zero. That is,

$$6/\omega RC - 1/R^3C^3\omega^3 = 0$$

which gives

$$\omega = 1/(\sqrt{6}RC) \tag{12.20}$$

Substituting the value of  $\omega$  in Eq. (12.19), we get expression for the feedback factor:

Feedback factor,

$$\beta = 1/(1-30)$$

(12.21)

This gives,

$$|\beta| = 1/29$$

(12.22)

Equations (12.20) and (12.22) specify the required conditions for loop phase shift and loop gain for RC phase shift oscillators employing lead-type RC phase shift network. The oscillation frequency is given by Eq. (12.20) and Eq. (12.22) tells that the amplifier gain must at least be equal to 29. Figure 12.5 shows circuit schematic of RC phase shift oscillator using lead-type phase shift network. The circuit uses opamp-based amplifier stage. The oscillator circuit using transistorized amplifier stage would be similar to the one shown in Figure 12.3 except for the feedback network.

To summarize, in the case of an RC phase shift oscillator, the frequency of oscillation is given by  $f = \sqrt{6}/(2\pi RC)$  if the feedback network employed lag-type RC sections and  $f = 1/(2\pi\sqrt{6}RC)$  if the feedback circuit used lead-type RC sections. Minimum amplifier gain in both cases is 29.

Figure 12.5 RC phase shift oscillator with lead-type feedback network using operational amplifier.

RC phase shift oscillator has limitations when it comes to designing a variable frequency oscillator as it is impractical to simultaneously vary three capacitance values equally. Also, adjustment of resistance values is not recommended because variation of resistance values will alter the loop gain of the oscillator circuit and there is likelihood of it not satisfying Barkhausen criterion for sustained oscillations. However, higher  $d\phi/d\omega$  resulting from steep phase versus frequency slope provided by the three-section RC network gives a reasonably high frequency stability.

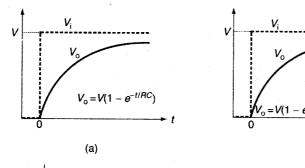

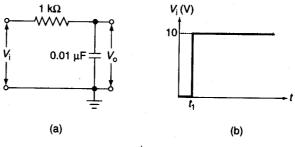

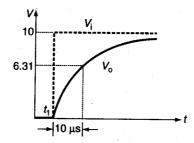

# 12.5 Buffered RC Phase Shift Oscillator

The buffered RC phase shift oscillator (Figure 12.6) overcomes the loading effect of different RC sections in the conventional phase shift oscillator. The oscillator performs very nearly at the computed values of

Figure 12.6 Buffered RC phase shift oscillator.

frequency and amplifier gain. The oscillation frequency in this case is given by Eq. (12.23) and the minimum value of the amplifier gain for sustained oscillations is 8.

$$f = \sqrt{3} / (2\pi RC) \tag{12.23}$$

In the case of lead-type RC network, the oscillation frequency would be given by

$$f = 1/(2\pi\sqrt{3}RC) \tag{12.24}$$

#### **EXAMPLE 12.2**

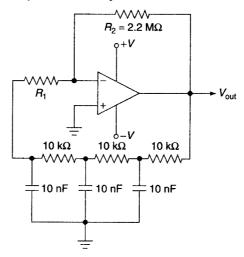

Refer to the phase shift oscillator of Figure 12.7. Determine the frequency at which this circuit would oscillate if the loop gain criterion were met. Also determine the maximum value of resistance  $(R_1)$  for sustained oscillations. How would the oscillation frequency change if the positions of R and C in the feedback network were interchanged?

Figure 12.7 | Example 12.2.

### Solution

- 1. The oscillation frequency (f) is given by  $f = \sqrt{6}/2\pi RC$ . Therefore,  $f = \sqrt{6}/2\pi RC$ .  $\sqrt{6/(6.283 \times 10 \times 10^3 \times 10 \times 10^{-9})} = 3.9 \text{ kHz}.$

- **2.** Minimum gain to be provided by the amplifier = 29.

- 3.  $|Gain| = R_2/R_1 = 29$ . 4. This gives  $R_1 = 2.2 \times 10^6/29 = 75.86 \text{ k}\Omega$ .

- 5.  $R_1$  should therefore be less than 75.86 k $\Omega$ .

- **6.** When the positions of R and C are interchanged, the oscillation frequency is given by  $f = 1/2\pi\sqrt{6}RC$ .

- 7. Substituting the values of R and C, we get f = 650 Hz.

#### **EXAMPLE 12.3**

If in the RC phase shift oscillator circuit of Example 12.2, the three RC sections were separated from each other by opamp buffers. First buffer is connected between the first and second RC sections; second buffer is connected between second and third RC sections and the third buffer is connected between the third RC section and the opamp input. Determine the new values of oscillation frequency and resistor (R, ) for sustained oscillations.

#### Solution

- 1. The oscillation frequency (f) in this case is given by  $f = \sqrt{3}/2\pi RC$ . Therefore,  $f = \sqrt{3}/(6.283 \times 10 \times 10^3 \times 10 \times 10^{-9}) = 2.758 \text{ kHz}.$

- 2. Minimum gain to be provided by the amplifier in this case is 8.

- 3. Therefore,  $R_1$  should be less than  $2.2 \times 10^6/8 = 275 \text{ k}\Omega$ .

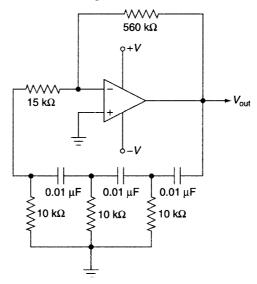

#### **EXAMPLE 12.4**

Figure 12.8 shows an RC phase shift oscillator using an opamp as the active device. The oscillator is oscillating at the correct frequency but the output is distorted severely near the signal peaks. What could be the possible causes?

Figure 12.8 Example 12.4.

#### Solution

- 1. The minimum amplifier gain requirement is 29.

- 2. In order to ensure that we get sustained oscillations and the device replacement and ageing have no effects, the amplifier gain is chosen to be slightly more than what is demanded by the Barkhausen criterion.

- 3. It may exceed the minimum required gain value by 10-15%. Too large a gain can cause signal clipping near the peaks.

- **4.** The gain magnitude in the present case is given by  $560 \times 10^3 / 15 \times 10^3 \cong 37.3$ , which exceeds the required minimum by approximately 30%. This explains the distortion observed in the output.

## 12.6 Bubba Oscillator

${f B}$  ubba oscillator is a slight variation of the buffered RC phase shift oscillator discussed in Section 12.5. Figure 12.9 shows the circuit schematic of the Bubba oscillator. The difference between the two is that the Bubba oscillator uses four RC sections in the feedback network with each RC section contributing a

Figure 12.9 Bubba oscillator.

phase difference of 45°. This offers two distinctive advantages. One, taking outputs from alternate sections yields low impedance quadrature outputs. Two, use of four RC sections provides higher  $d\phi/d\omega$ , which in turn leads to relatively higher frequency stability. The expression for the transfer function of the feedback network is given by Eq. (12.25). Remember that different sections in the feedback network are buffered and therefore there is no loading effect.

$$T(s) = \left[\frac{1}{1 + RCs}\right]^4 \tag{12.25}$$

Single RC section provides a phase shift of 45° for  $\omega = 1/RC$ . Substituting for  $\omega$  in Eq. (12.25) we get

$$\left|\beta\right| = \left|\frac{1}{(1+i)^4}\right| = \frac{1}{4}$$

(12.26)

Equation (12.26) tells that the gain of the amplifier must at least be 4 for oscillations to occur. As explained earlier, the gain is chosen to be 10–15% higher than this value.

# 12.7 Quadrature Oscillator

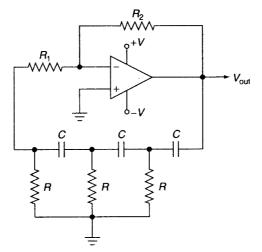

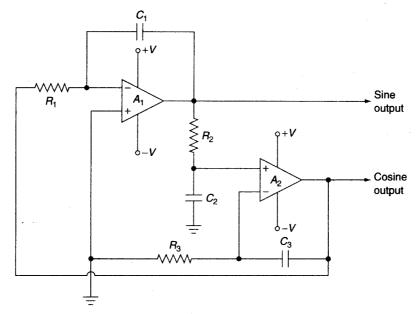

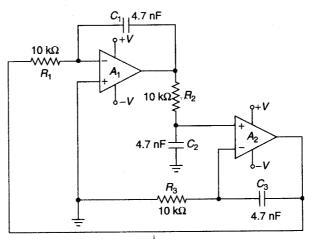

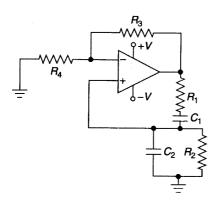

uadrature oscillator is yet another type of RC phase shift oscillator (Figure 12.10). As is evident from the circuit schematic of Figure 12.10, the circuit employs three RC sections. The circuit takes advantage

Figure 12.10 Quadrature oscillator.

of the fact that double integral of a sine wave is a negative sine wave of the same frequency and phase. This implies that the original waveform is 180° phase-shifted after double integration. The phase of the output from second integrator is then inverted to provide positive feedback to induce oscillations.

The transfer function of the feedback network is nothing but a cascade arrangement of a three networks. The first one comprises  $R_1-C_1$  configured around opamp  $A_1$ . The second one comprises  $R_2-C_2$  and the third one comprises  $R_3-C_3$  configured around opamp  $A_2$ . The expression for loop gain is given by

Loop gain =

$$\left[\frac{1}{R_1 C_1 s}\right] \times \left[\frac{1}{1 + R_2 C_2 s}\right] \times \left[\frac{1 + R_3 C_3 s}{R_3 C_3 s}\right]$$

(12.27)

If  $R_1C_1 = R_2C_2 = R_3C_3 = RC$  and if we substitute  $\omega = 1/RC$ , the first network provides a phase shift of 90°, the second and third networks provide phase shift of 45° so as to provide a total phase shift of 180°. Opamp  $A_1$  too provides a phase shift of 180°, which leads to loop phase shift of 0°. Also, Eq. (12.27) reduces to the following equation:

Loop gain =

$$\frac{1}{(RC_s)^2} = 1\angle -180^\circ$$

(12.28)

The circuit provides sine and cosine outputs (quadrature outputs) because of 90° phase difference between the two signals present at the outputs of the two opamps.

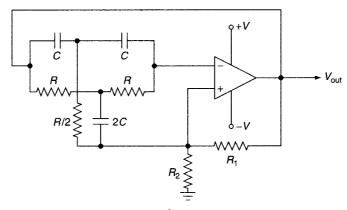

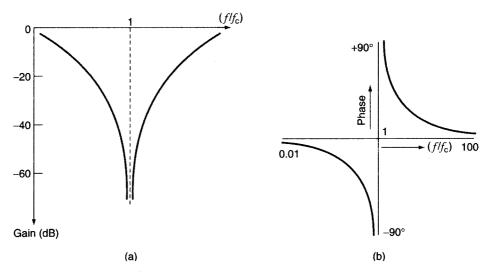

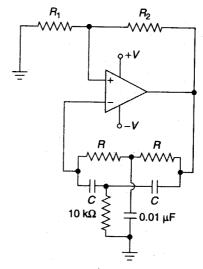

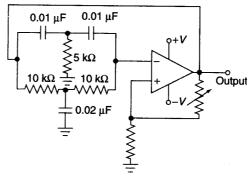

### 12.8 Twin-T Oscillator

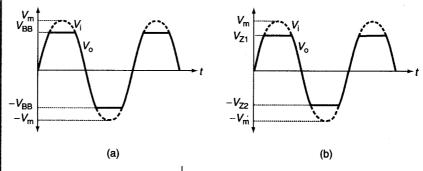

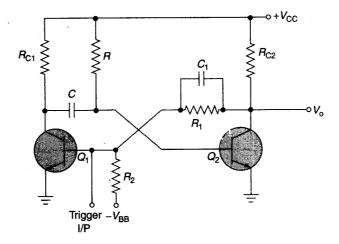

The Twin-T oscillator employs a twin-T-type of notch filter network as the frequency selective component in the feedback network. Figure 12.11 shows the basic circuit schematic of a Twin-T oscillator. The circuit employs both positive as well as negative feedback. The positive feedback necessary to produce oscillations is provided by a voltage divider network of  $R_1$  and  $R_2$ . The negative feedback is through the frequency selective twin-T network.

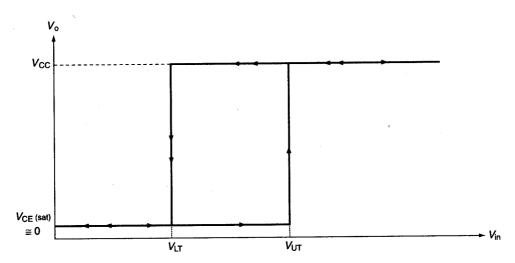

The operational principle of Twin-T oscillator can be best understood by analyzing its transfer function and thereby studying its magnitude and phase response as a function of frequency. In fact, twin-T network is a parallel connection of a lag-type T-network (lower T-network in Figure 12.11) and a lead-type T-network (upper T-network in Figure 12.11). The lag-type T-network causes the magnitude of transfer function to fall and the lagging phase shift angle to increase with increase in frequency. On the other hand, the lead-type T-network causes the magnitude of transfer function to increase and the leading phase shift angle to decrease with increase in frequency. At  $\omega = 1/RC$ , the two T-networks counter-balance each other with the result that both the magnitude as well as the phase of the transfer function tend to become zero. In fact, at  $\omega = 1/RC$ , decreasing amplitude response of the lag network counter-balances the increasing amplitude response of the lead network. Also, while lagging phase angle tends to become  $-90^{\circ}$ , the leading phase angle tends to become  $+90^{\circ}$ . Figure 12.12 shows the amplitude and phase response of the twin-T network as a function of normalized frequency.  $\omega_c$  equals 1/RC.

Figure 12.11 Twin-T oscillator.

Figure 12.12 (a) Magnitude; (b) phase response of twin-T network.

The same can be explained with the help of expression for transfer function of the twin-T network. Without going into mathematical details, the transfer function of the twin-T network can be expressed as

$$T(j\omega) = \frac{1 - \omega^2 R^2 C^2}{1 - \omega^2 R^2 C^2 + j4\omega CR}$$

(12.29)

The magnitude of  $T(j\omega)$  is

$$\left| T(j\omega) \right| = \frac{1 - \omega^2 R^2 C^2}{\sqrt{(1 - \omega^2 R^2 C^2)^2 + (4\omega C R)^2}}$$

(12.30)

The phase angle of  $T(i\omega)$  is

$$\theta = \tan^{-1}[4\omega CR/(1-\omega^2 C^2 R^2)]$$

(12.31)

Substituting  $\omega = 1/RC$  in Eqs. (12.30) and (12.31), we get the magnitude of transfer function as zero and the phase angle as either  $-90^{\circ}$  or  $+90^{\circ}$ . This small computation thus vindicates what was said in the preceding paragraph.

A zero amplitude for the transfer function implies zero negative feedback at  $\omega = 1/RC$ . The frequency corresponding to  $\omega = 1/RC$  is referred to as notch frequency. At all other frequencies, there will be very high negative feedback thus allowing the circuit to oscillate only very close to the notch frequency. Resistance  $R_2$  is a thermistor with a positive temperature coefficient. An incandescent lamp may also be used in place of thermistor. The positive temperature coefficient of resistance of tungsten filament used in incandescent lamp is used for the purpose. A low value of  $R_2$  initially produces a large amount of positive feedback to initiate oscillations. Once the oscillations build up, the current flowing through  $R_2$  heats it and thus raises its temperature. Increase in temperature increases the value of  $R_2$  thus reducing the positive feedback to stabilize the magnitude of oscillations.

Twin-T oscillator produces a low distortion sinusoidal output. This is primarily because of two reasons. First, harmonics are subjected to a very high level of negative feedback, thus severely attenuating them. Second, the operating point of the oscillator is very delicately balanced between positive and negative feedback. This necessitates a very small amount of non-linearity to stabilize the amplitude.

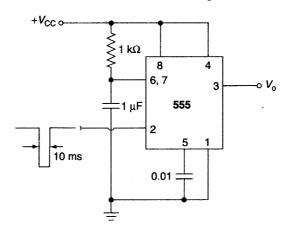

# 12.9 Wien Bridge Oscillator

The Wien bridge oscillator is the most widely used RC oscillator configuration for low-frequency applications due to simplicity of the circuit, very good frequency stability and its amenability to variable frequency operation. The only major disadvantage is its relatively higher amplitude distortion unless special measures are taken to minimize it. Modified Wien bridge oscillator designs that minimize distortion are also discussed in the subsequent paragraphs in this section. The basic Wien bridge oscillator circuit comprises a single-stage amplifier whose output is fed back to its input through a feedback network. The amplifier portion is usually implemented by an operational amplifier wired as a non-inverting amplifier. The feedback network comprises a cascade arrangement of a series RC and a parallel RC network. Figure 12.13 shows the circuit schematic of the basic Wien bridge oscillator configured around an operational amplifier.

In order to analyze the oscillator circuit of Figure 12.13, we need to analyze the transfer function of the feedback network. The transfer function will tell us about both the attenuation and the phase shift provided by this network as a function of frequency.

The transfer function of the feedback network can be computed as follows:

- 1. The impedance of series RC network =  $[R_1 + (1/C_1 s)]$ .

- **2.** Impedance of parallel RC network =  $[R_2/(1+R_2C_2s)]$ .

Figure 12.13 Basic Wien bridge oscillator.

The transfer function of the feedback network can therefore be written as

$$T(s) = \beta = \frac{R_2 / (1 + R_2 C_2 s)}{(R_1 + 1/C_1 s) + R_2 / (1 + R_2 C_2 s)}$$

(12.32)

Equation (12.32) can be simplified to

$$\beta = \frac{R_2 C_1 s}{R_1 C_1 R_2 C_2 s^2 + (R_1 C_1 + R_2 C_2 + R_2 C_1) s + 1}$$

(12.33)

Substituting  $s = j\omega$  in Eq. (12.33), we get

$$\beta = \frac{j\omega R_2 C_1}{(1 - \omega^2 R_1 C_1 R_2 C_2) + j\omega (R_1 C_1 + R_2 C_2 + R_2 C_1)}$$

(12.34)

The magnitude and phase responses of  $\beta$  are

Magnitude of

$$\beta$$

,  $|\beta| = \frac{\omega R_2 C_1}{\sqrt{(1 - \omega^2 R_1 C_1 R_2 C_2)^2 + \omega^2 (R_1 C_1 + R_2 C_2 + R_2 C_1)^2}}$  (12.35)

Phase angle,

$$\theta = 90^{\circ} - \tan^{-1}[\{\omega(R_1C_1 + R_2C_2 + R_2C_1)\}/(1 - \omega^2R_1C_1R_2C_2)]$$

(12.36)

In order that the loop phase shift is zero, the feedback network must provide a phase shift of zero only. From Eq. (12.36), this implies the following:

$$1 - \omega^2 R_1 C_1 R_2 C_2 = 0$$

which gives the frequency of oscillation as

$$\omega = \frac{1}{\sqrt{R_1 C_1 R_2 C_2}}$$

(12.37)

Substituting for  $\omega$  in Eq. (12.35) and simplifying, we get

$$\left|\beta\right| = \frac{R_2 C_1}{R_1 C_1 + R_2 C_2 + R_2 C_1} \tag{12.38}$$

If in the Wien bridge oscillator,  $R_1 = R_2 = R$  and  $C_1 = C_2 = C$ , then

$$|\beta| = 1/3 \tag{12.39}$$

This implies that the amplifier gain should at least be equal to 3. Also

$$\omega = \frac{1}{RC} \tag{12.40}$$

If we carefully examine the feedback network, we will notice that it is a combination of a lag network formed by  $R_1$  and  $C_2$  and a lead network formed by  $R_2$  and  $C_1$ . The operating frequency is the geometric mean of the two cut-off frequencies given by  $(1/2\pi R_1 C_2)$  and  $(1/2\pi R_2 C_1)$ .

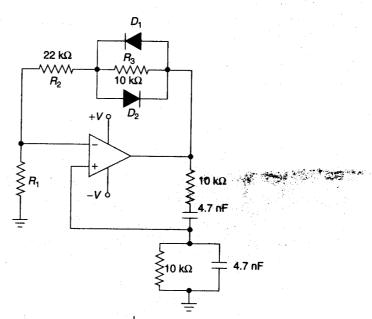

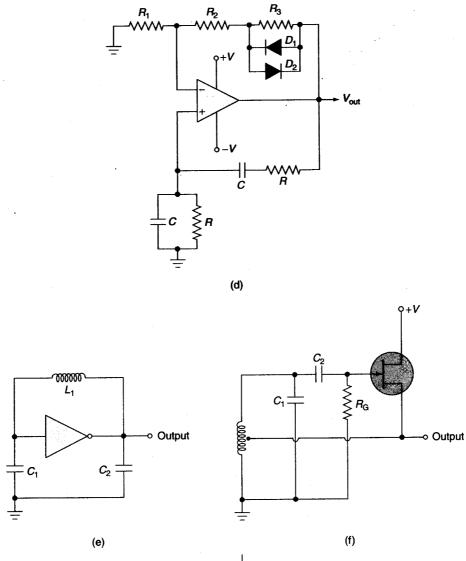

## Distortion in Wien Bridge Oscillator

As outlined earlier, Wien bridge oscillator is associated with relatively higher output distortion unless design measures are taken to minimize it. High output distortion results from the fact that the output amplitude is at power supply rails. This saturates the output transistors inside the opamp and causes clipping of the output signal at both the supply rails, thus producing several odd and even harmonics.

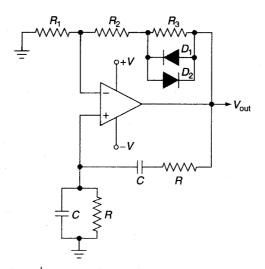

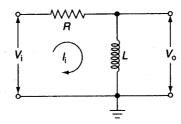

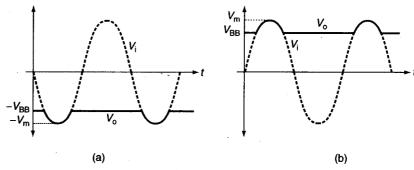

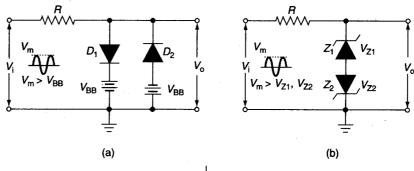

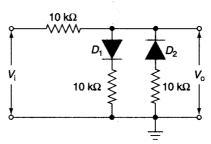

Distortion can be minimized by applying non-linear feedback. Figure 12.14 shows one such circuit. Initially, diodes  $D_1$  and  $D_2$  are non-conducting. The feedback resistance in that case is sum of  $R_2$  and  $R_3$ . For larger signals, voltage across  $R_3$  is large enough to make  $D_1$  and  $D_2$  conduct, respectively, during positive and negative half cycles. Conducting diodes  $(D_1 \text{ or } D_2)$  decrease effective  $R_3$ , thus reducing the gain.

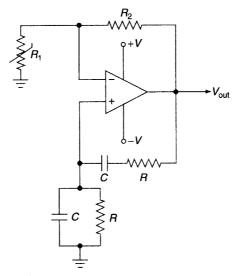

In another configuration, a non-linear component such as an incandescent lamp or a thermistor with positive temperature coefficient of resistance replaces the gain determining resistance connected from inverting input of the opamp to ground. Figure 12.15 shows the modified circuit schematic. The nominal value of resistance of the non-linear component is chosen to be equal to half of the feedback resistance at the current established by the two resistors. In the absence of any oscillations, the non-linear resistance value will be lower, causing the gain to be

Figure 12.14 | Wien bridge oscillator with non-linear feedback.

Figure 12.15 Wien bridge oscillator with a non-linear resistor.

greater than 3. This initiates oscillations. As the oscillations build up, the current through the non-linear resistance heats it up and causes its resistance to increase thus lowering the gain and stabilizing the output. The non-linear relationship between the current and the resistance ensures that a small change in output voltage causes a large change in the resistance value. This keeps the opamp output away from saturation and hence distortion is minimized. It is observed that the distortion in the circuit of the type shown in Figure 12.15 is more than an order of magnitude better than that observed in the case of oscillator circuit of Figure 12.13.

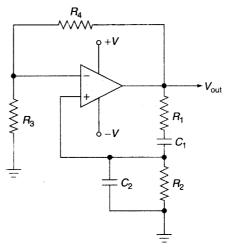

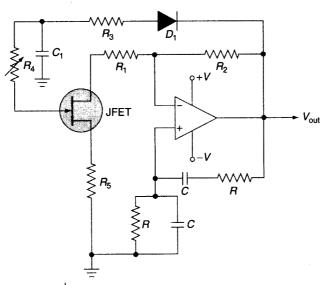

Another possible circuit configuration that achieves low level of output distortion is shown in Figure 12.16. The circuit employs an N-channel JFET whose drain-to-source ON-resistance  $R_{DS(ON)}$  is controlled by a

Figure 12.16 Wien bridge oscillator with automatic gain control.

negative gate voltage. This negative gate voltage is in turn proportional to the peak amplitude of the output signal. The drain-to-source resistance of the JFET is a part of the gain-determining network as is evident from the circuit. Any increase in output amplitude causes increased negative voltage at the JFET gate terminal. Increased negative voltage causes drain-to-source resistance to increase and therefore the gain to decrease. The circuit arrangement therefore provides automatic gain control. Various resistance values are so chosen as to have an initial gain of greater than 3 to start oscillations. Thereafter, the gain is automatically controlled.

#### **EXAMPLE 12.5**

Figure 12.17 shows a buffered RC oscillator circuit. Determine the following: (a) Frequency of oscillation.

- (b) Possible points in the circuit for quadrature outputs.

- (c) Value of resistance  $R_G$  (choose from 220 k $\Omega$ , 290 k $\Omega$ , 300 k $\Omega$  and 330 k $\Omega$ ).

#### Solution

- 1. The circuit shown is that of Bubba oscillator. It employs four RC sections isolated from each other with opamp buffers.

- 2. The frequency of oscillation is given by  $f = 1/2\pi RC$  as each of the four sections contributes a phase shift of 45°.

- 3. Therefore  $f = 1/(6.283 \times 10 \times 10^3 \times 10 \times 10^{-9}) = 1.592 \text{ kHz}.$

- **4.** Quadrature outputs may be taken from the outputs of opamps  $A_2$  and  $A_4$ . Remember outputs of  $A_2$  and  $A_4$  will be 90° apart.

- 5. Each RC section provides attenuation of  $(1/\sqrt{2})$  at the operating frequency.

- 6. Since RC sections are buffered, attenuation provided by feedback network will be  $(1/\sqrt{2})^4 = 1/4$ .

- 7. Therefore the gain of the amplifier should be slightly more than 4.

- 8. This implies that the input resistance  $R_{\rm G}$  should be slightly less than 300 k $\Omega$ . That is, 290 k $\Omega$  is the correct choice.

Figure 12.17 | Example 12.5.

## **EXAMPLE 12.6**

Figure 12.18 shows the circuit diagram of a Quadrature oscillator. Determine the operating frequency. Also determine the phase difference between the signals appearing at the outputs of opamps  $A_1$  and  $A_2$ . If the peak amplitude of the signal appearing at the output of  $A_1$  is 2 V, determine the peak amplitude of the signal at the junction of  $R_2$  and  $C_2$  and also at the output of  $A_2$ .

Figure 12.18 | Example 12.6.

#### Solution

- 1. The frequency of oscillation is given by  $f = 1/2\pi RC$ .

- 2. Substituting the values of R and C, we get

$$f = 1/(6.283 \times 10 \times 10^3 \times 4.7 \times 10^{-9}) = 3.386 \text{ kHz}$$

- 3. The transfer function from output of  $A_1$  to junction of  $R_2$ – $C_2$  is given by  $1/(1 + R_2C_2s)$ . At  $\omega = 1/R_2C_2$ , it produces a phase shift of  $-45^\circ$ .

- 4. The transfer function from junction of  $R_2$ - $C_2$  to the output of  $A_2$  is given by  $(1 + R_3C_3s)/R_3C_3s$ . At  $\omega = 1/R_3C_3$ , it produces a phase shift of -45°. Since  $R_2C_2 = R_3C_3$ , the phase shift from output of  $A_1$  to the output of  $A_2$  will be -90°.

- 5. It is clear from the transfer functions mentioned above that the two networks respectively provide attenuation and gain of  $1/\sqrt{2}$  and  $\sqrt{2}$ .

- **6.** Therefore, peak amplitude of signal at junction of  $R_2 C_2$  is  $2/\sqrt{2} = \sqrt{2}$  V and that at the output of  $A_2$  is  $\sqrt{2} \times \sqrt{2} = 2$  V.

#### **EXAMPLE 12.7**

Refer to the Twin-T oscillator of Figure 12.19. Determine the frequency of the output signal. How would the frequency change if all component values in the twin-T network are doubled?

#### Solution

- 1. The operating frequency (f) is given by  $f = 1/2\pi RC$ .

- 2. If we compare the given twin-T network with the standard form of twin-T, we will find that  $R=2\times10\times10^3~\Omega=20~k\Omega$  and  $C=0.01\times10^{-6}/2=0.005~\mu F$ .

- 3. Therefore,  $f = 1/(6.283 \times 20 \times 10^3 \times 0.005 \times 10^{-6}) = 1.592 \text{ kHz}.$

Figure 12.19 | Example 12.7.

When all component values are doubled, the operating frequency will be reduced to one-fourth. That is, changed value of frequency = 1.592/4 = 398 Hz.

## **EXAMPLE 12.8**

Refer to the Wien bridge oscillator circuit of Figure 12.20. Determine the oscillator frequency and the preferred value of R<sub>1</sub>.

Figure 12.20 | Example 12.8.

## Solution

- 1. Oscillator frequency is given by  $f = 1/2\pi RC$  where  $R = 10 \text{ k}\Omega$  and C = 4.7 nF.

- 2. Therefore,  $f = 1/(6.283 \times 10 \times 10^3 \times 4.7 \times 10^{-9}) = 3.386 \text{ kHz}.$

- 3. Required minimum value of amplifier gain = 3.

- **4.** Amplifier gain =  $1 + [(R_2 + R_3)/R_1]$ .

- 5. This gives  $(R_2 + R_3)/R_1 = 2$ ,  $R_1 = (22 \times 10^3 + 10 \times 10^3)/2 = 16 \times 10^3 \Omega = 16 \text{ k}\Omega$ .

- **6.** Since the required gain has to be slightly greater than 3, preferred value of  $R_1$ therefore should be slightly less than 16 k $\Omega$ .

- 7.  $R_1$  may be chosen to be 15 k $\Omega$ .

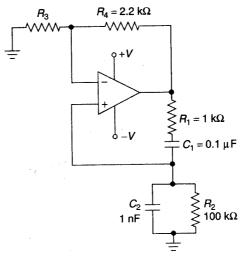

## **EXAMPLE 12.9**

Refer to the RC oscillator circuit of Figure 12.21. Identify the type of oscillator. Also, determine the operating frequency and preferred value of  $R_3$ .

### **Solution**

- 1. It is Wien bridge oscillator.

- 2. Operating frequency is given by  $\omega = 1/\sqrt{R_1R_2C_1C_2}$ . Therefore,  $\omega =$  $1/\sqrt{10^3 \times 100 \times 10^3 \times 0.1 \times 10^{-6} \times 10^{-9}} = 10^4 \text{ rad/s}.$

- 3.  $f = \omega/2\pi = 10^4/6.283 \text{ Hz} = 1.592 \text{ kHz}.$

- 4. Attenuation provided by feedback network is given by

$$|\beta| = R_2 C_1 / (R_1 C_1 + R_2 C_2 + R_2 C_1)$$

$$|\beta| = (100 \times 10^3 \times 0.1 \times 10^{-6}) / (10^3 \times 0.1 \times 10^{-6} + 100 \times 10^3 \times 10^{-9} + 100 \times 10^3 \times 0.1 \times 10^{-6})$$

$$= 10^{-2} / (10^{-4} + 10^{-4} + 10^{-2}) = 1/1.02$$

- 5. Therefore, minimum value of required gain = 1.02. That is,  $1 + (R_4/R_3) = 1.02$ ,  $R_{\rm A}/R_{\rm 3}=0.02$ .

- 6.  $R_3 = 2.2 \times 10^3 / 0.02 = 110 \text{ k}\Omega.$

- 7. Since the required gain has to be slightly greater than 1.02, preferred value of  $R_3$  therefore should be slightly less than 110 k $\Omega$ .

- **8.**  $R_3$  may be chosen to be 100 k $\Omega$ .

Figure 12.21 | Example 12.9.

### 12.10 LC Oscillators

s outlined earlier, in essence, every oscillator has three main sections. These are the amplifier, the frequency $oldsymbol{A}$  determining network and the feedback arrangement. The frequency-determining network decides the operating frequency and the feedback arrangement ensures that part of the output signal fed back to the input has the correct amplitude and phase at the operating frequency. In fact, the feedback network together with the amplifier ensures that Barkhausen criterion for sustained oscillations is satisfied at the operating frequency.

In the case of LC oscillators, the operating frequency is determined by an LC tank circuit and is given by  $(1/2\pi\sqrt{LC})$ . The exact frequency of oscillation is determined by  $(1/2\pi\sqrt{LC}) \times \sqrt{Q^2/(Q^2+1)}$ . Here Q is the quality factor of the tank circuit. The amplifier may be configured around a bipolar transistor, a junction FET, a MOSFET or an operational amplifier.

LC oscillators are usually classified by the name of its inventor. The common ones are Armstrong oscillator, Hartley oscillator, Colpitt oscillator and Clapp oscillator. They are also classified as series-fed or shunt-fed oscillators depending upon the manner in which DC power is applied to the active device. In the case of series-fed LC oscillators, DC power is applied to the active device through the tank circuit or a part of the tank circuit. In shunt-fed LC oscillators, DC power is applied through a separate path that is parallel to the tank circuit. Each of the LC oscillators mentioned in the preceding paragraph can be constructed either way.

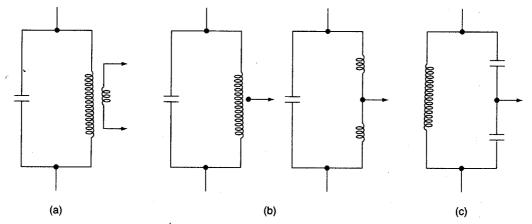

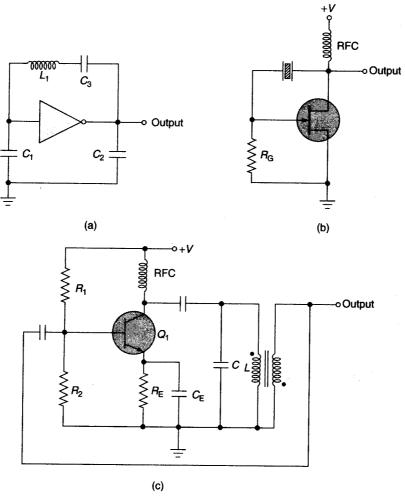

Also, LC oscillators (Armstrong, Hartley, Colpitt and Clapp) are identifiable by the manner in which feedback signal is coupled to the input. In the case of Armstrong oscillator, the feedback signal is magnetically coupled [Figure 12.22(a)]. In the case of Hartley oscillator, a tapped or a split coil is used for the purpose [Figure 12.22(b)]. Split capacitor arrangement is used in the case of Colpitt and Clapp oscillators [Figure 12.22(c)]. Each of these oscillators is described in the following sections.

Figure 12.22 | Feedback coupling arrangement in LC oscillators.

# 12.11 Armstrong Oscillator

rmstrong oscillator, also known as Meissner oscillator, uses magnetic coupling as means of feeding Apart of output signal back to input to provide oscillations. It is also called a Tickler oscillator due to use of magnetic coupling between the tickler coil and the coupling coil. Tickler coil is the name given to a small coil connected in series with the plate circuit of a vacuum tube and coupled inductively to the grid circuit to provide feedback. In the case of a BJT or an FET, the tickler coil is placed in series with the collector or drain circuit and is inductively coupled to the base or gate circuit. A capacitor is placed across either the coupling coil or the tickler coil to form a tank circuit that decides the operating frequency.

Figures 12.23(a) and (b) show the basic circuit arrangements in the two cases with n-channel junction FET used as the active device. Biasing components are omitted for the sake of simplicity.

The frequency of oscillation is primarily determined by the tank circuit and is given by

$$f = \frac{1}{2\pi\sqrt{LC}}\tag{12.41}$$

Here L is the inductance of the coupling coil in the case of circuit shown in Figure 12.23(a) and that of tickler coil in the case of circuit shown in Figure 12.23(b). In practice, the frequency of oscillations is slightly different from the one computed by using Eq. (12.41) because of stray capacitances, loading of tank circuit, etc. The feedback factor in this case is given by ratio of mutual inductance between the two coils to the inductance in the tank circuit. Minimum gain required to start oscillations is reciprocal of the feedback factor.

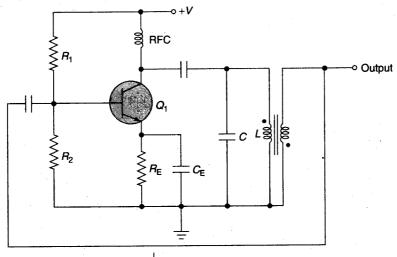

Figure 12.24 shows the circuit schematic of an Armstrong oscillator configured around a bipolar junction transistor. The transistor is wired in common-emitter configuration and thus provides a phase shift of

Figure 12.23 | Basic Armstrong oscillator configurations.

Figure 12.24 | Shunt-fed Armstrong oscillator.

Figure 12.25 | Series-fed Armstrong oscillator.

$180^{\circ}$ . Another  $180^{\circ}$  phase shift is provided by magnetic coupling as indicated by placement of dots. Operating frequency is decided by tank circuit comprising capacitor C and inductance L of transformer primary. Note that Armstrong oscillator of Figure 12.24 is a shunt-fed oscillator. The circuit schematic of a series-fed Armstrong oscillator would look like the one shown in Figure 12.25.

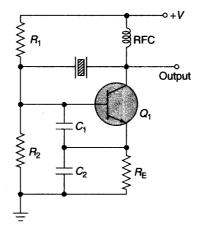

# 12.12 Hartley Oscillator

Hartley oscillator uses a tapped or split coil for the purpose of generating feedback signal. This is where a Hartley oscillator differs from an Armstrong oscillator, which uses a separate coil called tickler coil. In the case of Hartley oscillator, current flowing through one section of the tapped coil induces a voltage in the other section to provide feedback. The feedback signal is 180° out-of-phase with the one that produces it.

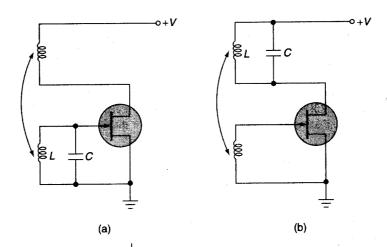

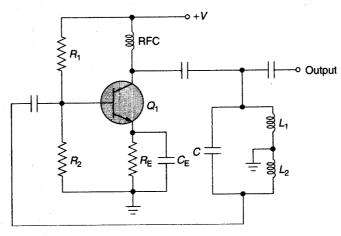

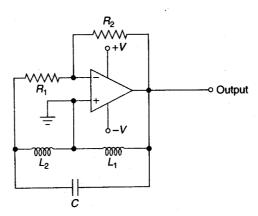

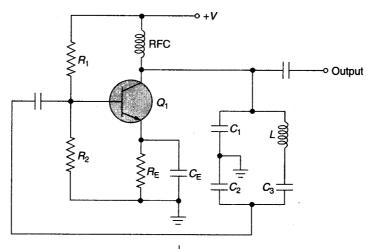

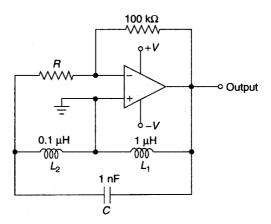

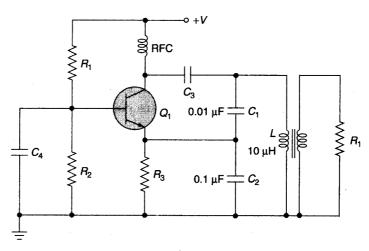

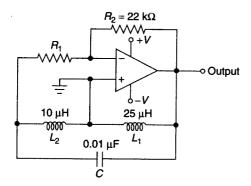

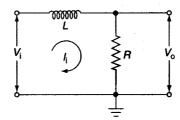

Figure 12.26 shows the circuit schematic of Hartley oscillator configured around a bipolar junction transistor. Incidentally, the circuit shown is that of a series-fed oscillator. Figure 12.27 shows the Hartley oscillator configured around an opamp.

The attenuation factor and the phase shift provided by the feedback network can be determined from the transfer function of the feedback network. The feedback network in the present case is a  $\pi$ -network with capacitive series element and inductive shunt elements. The transfer function is given by

$$T(j\omega) = \beta = \frac{-\omega^2 L_2 C}{1 - \omega^2 L_2 C} = \frac{-(1 - \omega^2 L_1 C)}{\omega^2 L_1 C}$$

(12.42)

Negative sign implies phase shift of 180°. Also,

$$\left|\beta\right|^{2} = \left[\frac{\omega^{2} L_{2} C}{1 - \omega^{2} L_{2} C}\right] \times \left[\frac{1 - \omega^{2} L_{1} C}{\omega^{2} L_{1} C}\right]$$

$$= \left(\frac{L_{2}}{L_{1}}\right) \times \left[\frac{1 - \omega^{2} L_{1} C}{1 - \omega^{2} L_{2} C}\right]$$

Figure 12.26 | Hartley oscillator configured around bipolar junction transistor.

Substituting  $\omega = 1/\sqrt{(L_1 + L_2)C}$ , we get

$$\left|\beta\right|^{2} = \left(\frac{L_{2}}{L_{1}}\right)^{2}$$

$$\left|\beta\right| = \left(\frac{L_{2}}{L_{1}}\right)$$

(12.43)

Equations (12.42) and (12.43) imply that the feedback network introduces a phase shift of 180° and signal attenuation by a factor of  $(L_2/L_1)$  at the operating frequency ( $\omega$ ) provided that  $\omega = 1/\sqrt{(L_1 + L_2)C}$ . This further implies that the amplifier must provide a gain of greater than  $L_1/L_2$  to satisfy the loop gain criterion and a phase shift of 180° to satisfy the loop phase shift criterion.

The advantage of using Hartley oscillator lies in its capability to generate a wide range of frequencies and its easy tunability.

Figure 12.27 Hartley oscillator configured around opamp.

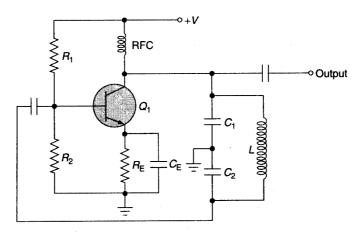

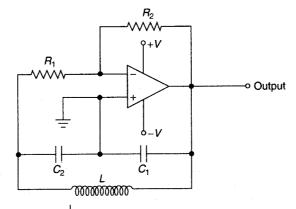

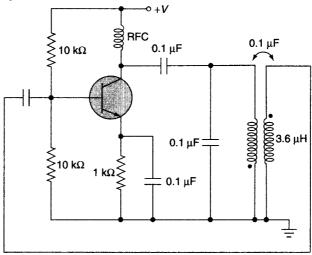

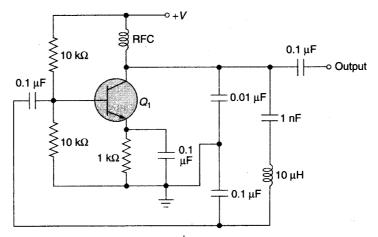

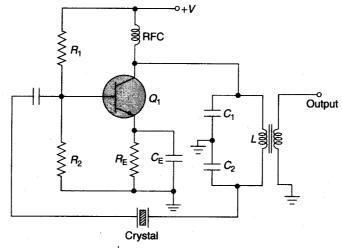

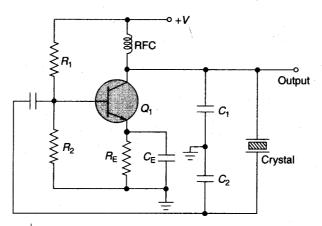

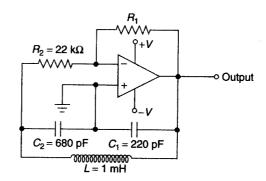

# 12.13 Colpitt Oscillator

Colpitt oscillator uses a pair of capacitors and an inductor in the tank circuit to produce the regenerative-feedback signal. In fact, the feedback network in this case is an electrical dual of the feedback network of Hartley oscillator. Figures 12.28 and 12.29 show the Colpitt oscillator circuits configured around bipolar junction transistor and opamp, respectively. An FET could also be used as the active device instead. As is obvious from the two circuit schematics, the output signal is developed across  $C_1$  and the feedback signal is generated across  $C_2$ .

The attenuation factor and the phase shift provided by the feedback network can be determined from the transfer function of the feedback network. The feedback network in the present case is a  $\pi$ -network with inductive series element and capacitive shunt elements. The transfer function is given by

$$T(j\omega) = \beta = -(\omega^2 L C_1 - 1) = \frac{-1}{\omega^2 L C_2 - 1}$$

(12.44)

Negative sign implies phase shift of 180°. We will subsequently see that for  $\omega = 1/\sqrt{LC_1C_2/(C_1+C_2)}$ , both  $(\omega^2LC_1-1)$  and  $(\omega^2LC_2-1)$  are positive.

Figure 12.28 Colpitt oscillator configured around bipolar transistor.

Figure 12.29 Colpitt oscillator configured around opamp.

Also,

$$\left|\beta\right|^2 = \frac{\omega^2 L C_1 - 1}{\omega^2 L C_2 - 1}$$

For  $\omega = 1/\sqrt{LC_1C_2/(C_1+C_2)}$ , this simplifies to

$$\left|\beta\right| = \frac{C_1}{C_2} \tag{12.45}$$

Equations (12.44) and (12.45) imply that the feedback network introduces a phase shift of 180° and signal attenuation by a factor of  $C_1/C_2$  at the operating frequency ( $\omega$ ) provided that  $\omega = 1/\sqrt{LC_1C_2/(C_1+C_2)}$ . This further implies that the amplifier must provide a gain of greater than  $(C_2/C_1)$  to satisfy the loop gain criterion and a phase shift of 180° to satisfy the loop phase shift criterion.

In practice, the operating frequency is affected by the junction capacitance whose Miller components appear across  $C_1$  and  $C_2$ . This is overcome in Clapp oscillator configuration.

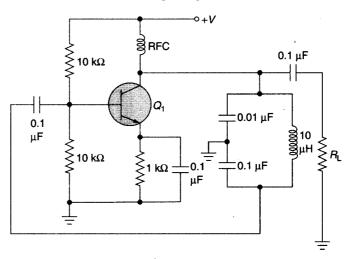

# 12.14 Clapp Oscillator

Clapp oscillator circuit is a slight modification of the Colpitt oscillator circuit configuration. The feedback circuit in the case of Clapp oscillator uses an extra capacitor ( $C_3$  in Figure 12.30) in series with the coil. The function of  $C_3$  is to minimize the effect of junction capacitance on the operating frequency.

The operating frequency (f) is given by

$$f = \frac{1}{2\pi} \times \sqrt{\frac{1}{L} \times \left\{ \left( \frac{1}{C_1} \right) + \left( \frac{1}{C_2} \right) + \left( \frac{1}{C_3} \right) \right\}}$$

(12.46)

If  $C_3$  is chosen to be much smaller than either  $C_1$  or  $C_2$ , then expression for frequency (f) simplifies to

$$f = \frac{1}{2\pi\sqrt{LC_3}}\tag{12.47}$$

Figure 12.30 Clapp oscillator.

Remember that we still need  $C_1$  and  $C_2$  to provide the required phase shift for regenerative feedback. Clapp oscillator is preferred over Colpitt oscillator for designing variable frequency oscillators. The adjustment of tuning element ( $C_3$  in Clapp oscillator) does not alter the attenuation factor in Clapp oscillator. The attenuation factor is decided by  $C_1$  and  $C_2$ . In the case of Colpitt oscillator, any attempt to vary the frequency by varying either  $C_1$  or  $C_2$  might cause cessation of oscillations over a portion of desired frequency range.

#### **EXAMPLE 12.10**

Refer to the Armstrong oscillator circuit of Figure 12.31. Determine (a) frequency of oscillations and (b) minimum amplifier gain required to start oscillations. How would the oscillation frequency change if the loaded Q-factor of the tank circuit were given to be 5?

Figure 12.31 Example 12.10.

#### Solution

- 1. Frequency of oscillations,  $f = 1/2\pi\sqrt{LC} = 1/(6.283\sqrt{3.6} \times 10^{-6} \times 0.1 \times 10^{-6})$ = 265.3 kHz.

- **2.** Feedback factor =  $0.1 \times 10^{-6}/3.6 \times 10^{-6} = 1/36$ .

- 3. Therefore, minimum value of amplifier gain required to start oscillations = 36.

- **4.** Q-factor of the tank circuit = 5.

- **5.** Frequency of oscillation will reduce by a factor equal to  $\sqrt{Q^2/(Q^2+1)}$ .

- **6.** Therefore, new frequency of oscillations will be  $265.3 \times 10^3 \times \sqrt{5^2/(5^2+1)} = 260.1 \text{ kHz}.$

#### **EXAMPLE 12.11**

Refer to the Colpitt oscillator of Figure 12.32. Determine (a) frequency of oscillations and (b) minimum gain required to start oscillations.

#### Solution

- 1. Equivalent value of capacitance, C, in the tank circuit  $C = 0.1 \times 10^{-6} \times 0.01 \times 10^{-6}/(0.1 \times 10^{-6} + 0.01 \times 10^{-6}) = 0.009 \ \mu F$

- 2. Inductance,  $L = 10 \mu H$ .

- 3. Therefore, frequency of oscillations,  $f = 1/(2\pi\sqrt{10\times10^{-6}\times0.009\times10^{-6}}) = 530.5 \text{ kHz}.$

- **4.** Feedback factor =  $0.01 \times 10^{-6}/0.1 \times 10^{-6} = 1/10$ .

- 5. Therefore, minimum value of amplifier gain = 10.

Figure 12.32 Example 12.11.

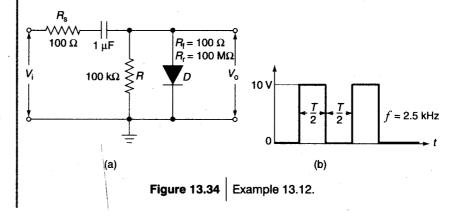

### EXAMPLE 12.12

Refer to the Hartley oscillator of Figure 12.33. Determine (a) operating frequency and (b) maximum acceptable value of resistance (R) for oscillations to start.

Figure 12.33 Example 12.12.

#### Solution

- 1. Frequency of oscillations is given by  $f = 1/2\pi\sqrt{LC}$ .

- 2.  $L = L_1 + L_2 = 1.0 \times 10^{-6} + 0.1 \times 10^{-6} = 1.1 \,\mu\text{H}$  and  $C = 1 \,\text{nE}$

- 3. Therefore,  $f = 1/(6.283 \times \sqrt{1.1 \times 10^{-6} \times 1 \times 10^{-9}}) = 4.799 \text{ MHz}.$

- **4.** Feedback factor =  $(0.1 \times 10^{-6})/(1.0 \times 10^{-6}) = 0.1$ .

- 5. Therefore, minimum required gain = 10.

- **6.** Now,  $|gain| = 100 \times 10^3 / R$ .

- 7. Therefore maximum value of  $R = 10^5/10 = 10^4 \Omega = 10 \text{ k}\Omega$ .

#### EXAMPLE 12.13

Refer to the Colpitt oscillator of Figure 12.32. The circuit is slightly modified by connecting an additional capacitor of 1.0 nF in series with the inductance (L) as shown in Figure 12.34. Does the modified oscillator configuration resemble any standard oscillator configuration? Determine frequency of oscillations in this case.

Figure 12.34 | Example 12.13.

## Solution

- 1. The modified circuit is the Clapp oscillator configuration.

- **2.** The frequency of oscillations is given by  $f = 1/2\pi\sqrt{LC}$ .

- 3. In the present case, C, is given by  $1/C = (1/C_1) + (1/C_2) + (1/C_3)$ .

- **4.** Substituting for  $C_1$ ,  $C_2$  and  $C_3$ , we get  $1/C = 1/(0.01 \times 10^{-6}) + 1/(0.1 \times 10^{-6}) + 1/(1 \times 10^{-9})$ .

- 5. This gives  $C = 0.0009 \,\mu\text{F}$ .

- **6.** Therefore,  $f = 1/(6.283 \times \sqrt{10 \times 10^{-6} \times 0.0009 \times 10^{-6}}) = 1.677 \text{ MHz}.$

#### **EXAMPLE 12.14**

Refer to the oscillator of Figure 12.35. Does the given oscillator circuit resemble any standard oscillator configuration? If yes, identify the oscillator configuration. Also, determine its frequency of oscillations and the required minimum value of amplifier gain.

Figure 12.35 | Example 12.14.

### **Solution**

- If we carefully examine the given circuit, we find that it follows the Colpitt oscillator configuration.

- 2. The feedback circuit in this case is also a tank circuit comprising a pair of series connected capacitors  $C_1$  and  $C_2$  and an inductor L.

- 3. Also, the amplifier has been wired in common-base configuration. Note that the base terminal is effectively grounded for AC signal through capacitor  $C_4$ .

- The output in this case appears across series combination of  $C_1$  and  $C_2$ . It appeared across  $C_1$  only in the case of Colpitt oscillator configured around common-emitter amplifier. The feedback signal appears across  $C_2$  in both the

- **5.** The feedback factor in this case is therefore given by  $[C_1 \times C_2/(C_1 + C_2)]/C_2$ , which simplifies to  $C_1/(C_1 + C_2)$ .

- **6.** The required minimum value of amplifier gain is therefore  $(C_1 + C_2)/C_1$ .

- 7. Frequency of oscillations can be computed from  $f = 1/2\pi\sqrt{LC}$ , where 7. Requests, or estimated at  $C = C_1 \times C_2/(C_1 + C_2)$ . 8. Now  $C = 0.01 \times 10^{-6} \times 0.1 \times 10^{-6}/(0.01 \times 10^{-6} + 0.1 \times 10^{-6}) = 0.009 \,\mu\text{F}$ . 9. Therefore,  $f = 1/2\pi\sqrt{10\times10^{-6}\times0.009\times10^{-6}} = 530.5 \,\text{kHz}$ .

- **10.** Feedback factor =  $0.01 \times 10^{-6}/(0.01 \times 10^{-6} + 0.1 \times 10^{-6}) = 1/11$ .

- 11. Also, required minimum value of amplifier gain = 11.

# 12.15 Crystal Oscillator

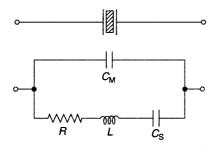

Tn the case of a crystal oscillator, a quartz crystal with the desired value of resonant frequency forms part of the f Ifrequency-selective feedback network. Crystal oscillator is the natural choice when the accuracy and stability of oscillation frequency is of paramount importance. In order to understand the operation of crystal oscillators, it is important that we first study and analyze the AC equivalent circuit of the crystal as a component.

## AC Equivalent Circuit of a Quartz Crystal

Figure 12.36 shows the circuit representation and AC equivalent circuit of the quartz crystal. R, L and  $C_{\rm S}$ , respectively, represent the resistance, inductance and capacitance of the piezoelectric crystal element.  $C_{\rm M}$  represents the mounting capacitance. It is in fact the capacitance due to the parallel-plate capacitor formed by the connecting electrodes and the piezoelectric element constituting the dielectric. Typically, R is in the range of few hundreds of ohms to a few kilo-ohms; L is of the order of few tens of milli-henries to few henries,  $C_{\rm S}$  is a very small fraction of a pico-farad and  $C_{\rm M}$  is few pico-farads. The Q-factor of the crystal is given by  $Q = \omega L/R = 1/\omega C_{\rm S} R$ .

The crystal exhibits two resonant frequencies. One is the series resonant frequency  $f_S$ . It is the frequency at which the inductive reactance of inductance L equals the capacitive reactance of capacitance  $C_S$ . It is expressed as

$$f_{\rm S} = \frac{1}{2\pi\sqrt{LC_{\rm S}}}\tag{12.48}$$

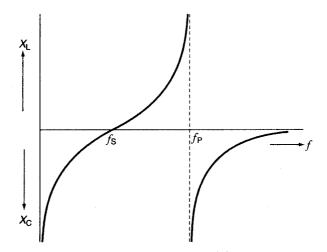

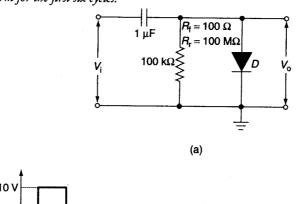

Figure 12.37 shows the plot of reactance versus frequency for the equivalent circuit of Figure 12.36. Quite understandably, the impedance is a capacitive reactance below the series resonant frequency and an

Figure 12.36 | Circuit representation and AC equivalent circuit of a quartz crystal.

Figure 12.37 Reactance versus frequency plot of a quartz crystal.

inductive reactance above it. The second resonant frequency called the parallel resonant frequency  $(f_p)$ occurs at a value where the inductive reactance equals the capacitive reactance due to equivalent capacitance of the tank circuit. Parallel resonance occurs at a frequency where the circulating loop current is at its maximum. Since circulating loop current flows through series combination of  $C_S$  and  $C_M$ , therefore the equivalent capacitance of the parallel tuned circuit is given by

$$C_{\rm P} = \frac{C_{\rm M} \times C_{\rm S}}{C_{\rm M} + C_{\rm S}} \tag{12.49}$$

Parallel resonant frequency is given by

$$f_{\rm P} = \frac{1}{2\pi\sqrt{LC_{\rm P}}}\tag{12.50}$$

Since  $C_S$  is much smaller than  $C_M$ ,  $C_P$  is only marginally less than  $C_S$  with the result that  $f_S$  and  $f_P$  are very close to each other. The apparent difference between  $f_S$  and  $f_D$  as shown in Figure 12.37 is an exaggerated one to explain the operation of the crystal.

The two resonant frequencies described in the previous paragraph are the fundamental resonant frequencies. Remember that the specified crystal frequency is between  $f_S$  and  $f_P$ . This area of frequencies between  $f_S$ and  $f_p$  is known as the area of usual parallel resonance or simply the area of parallel resonance. A crystal can also resonate at harmonics of the fundamental frequency called overtones. The fundamental resonant frequency of the crystal is usually limited to less than 30 MHz due to the smallest physical dimension the crystal can be cut to. Operation in the overtone mode allows stable output at much higher frequencies.

## Extremely High Frequency Stability

The extremely high frequency stability of a crystal oscillator comes from its extremely stable values of inductance and capacitance and a very high value of its Q-factor. Remember that the oscillation frequency of an LC oscillator in addition to the values of L and C also depends upon the Q-factor of the LC circuit. The generalized expression is given by

$$f = [1/(2\pi\sqrt{LC})] \times \sqrt{Q^2/(Q^2 + 1)}$$

(12.51)

A very high value of Q-factor in the case of quartz crystal ensures that the stability of oscillation frequency exclusively depends upon the operational stability of crystal elements. As a component, crystal is extremely stable.

A high value of Q-factor also produces a high value of rate of change of phase with respect to frequency  $(d\theta/d\omega)$ , where  $\theta$  represents phase. It implies that even infinitesimally small change in  $\omega$  will produce a sufficient change in  $\theta$  to restore the frequency to the original value. In general, the frequency-determining network of an oscillator should be made up of elements with extremely high operational stability and its Q-factor should be high. On both these accounts, quartz crystal has no competitor. It has Q-factor approaching tens of thousands and as a component, it is extremely stable.

## Crystal Oscillator Circuits

As is evident from the impedance versus frequency characteristics of a crystal, depending upon the circuit characteristics, it can act like a capacitor, an inductor, a series-tuned circuit or a parallel-tuned circuit. There are a large number of crystal oscillator configurations depending upon the mode in which the crystal is used. In one of the categories of crystal oscillator, crystal is connected in series with the LC tank circuit in the feedback path. Each of the LC oscillator circuits discussed in Section 12.14 (Armstrong, Hartley, Colpitt and Clapp) can be configured as a crystal-controlled oscillator by connecting a crystal in series with the tank circuit.

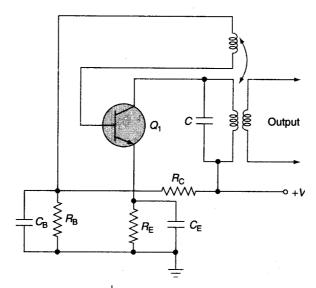

Figure 12.38 | Crystal-controlled Colpitt oscillator.

Figure 12.38 shows one such oscillator circuit. It is the modified Colpitt oscillator circuit. The circuit operates as follows. The *LC* tank circuit is tuned to the series resonant frequency of the crystal. The crystal offers minimum impedance at the series resonant frequency and thus allows the feedback signal to reach the input with practically no additional attenuation. A slight variation in frequency introduces very high impedance. The feedback signal is further attenuated to an extent that loop gain criterion is not met and the oscillations stop. Thus the oscillator can oscillate only at the resonant frequency of the crystal, thus significantly improving the frequency stability of the oscillator. Armstrong, Hartley and Clapp oscillator circuits can similarly be modified by introducing a quartz crystal in series with the respective tank circuits.

Figure 12.39 shows another variation of crystal-controlled Colpitt oscillator circuit. Here crystal forms a part of the tank circuit. The crystal acts like an inductor that resonates with capacitors  $C_1$  and  $C_2$ . The resonant frequency is somewhere between the series and parallel resonant frequencies of the quartz crystal.

Figure 12.39 Crystal-based Colpitt oscillator with common-emitter amplifier.

Figure 12.40 Crystal-based Colpitt oscillator with common-base amplifier.

Figure 12.40 shows a slightly modified Colpitt oscillator circuit that uses common-base amplifier configuration instead of common-emitter configuration used in the oscillator circuit of Figure 12.39. Common-base amplifier configuration allows operation at relatively higher oscillation frequencies.

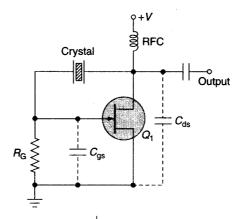

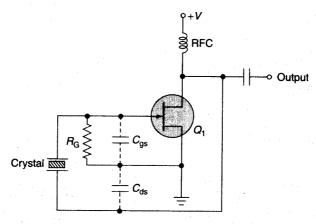

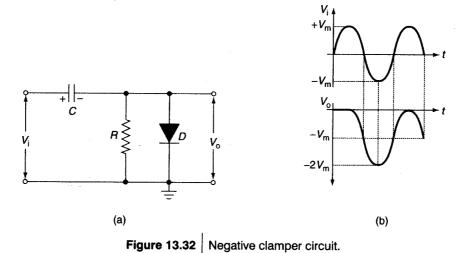

Yet another application of Colpitt oscillator configuration is found in what is popularly known as *Pierce oscillator*. Figure 12.41 shows the basic circuit implementation of a Pierce oscillator. An FET (JFET or MOSFET) is used as the active device and the crystal along with the inter-electrode capacitances  $C_{\rm gs}$  and  $C_{\rm ds}$  constitute the feedback network. Pierce oscillator of Figure 12.41 is redrawn in Figure 12.42 to demonstrate its resemblance to Colpitt oscillator configuration. The oscillation frequency is the parallel resonant frequency of the crystal and the inter-electrode capacitances do not play any role in determining oscillation frequency. The feedback factor and therefore the required amplifier gain are determined by  $C_{\rm gs}$  and  $C_{\rm ds}$ . In fact, it is observed that the oscillator stops oscillating as the oscillation frequency is reduced to below about 2 MHz due to insufficient feedback. In a situation like this, it becomes imperative to have external capacitors between gate-source and drain-source terminals. Pierce oscillator works very well in very high frequency (VHF) and ultra high frequency (UHF) frequency ranges. Purpose of putting radio-frequency choke (RFC) is to prevent the high-frequency output from getting grounded through drain power supply.

Figure 12.41 Basic Pierce oscillator.

Basic Pierce oscillator

### **EXAMPLE 12.15**

A quartz crystal is characterized by L = 2.5 H, R = 1 k $\Omega$ ,  $C_{\rm S}$  = 0.01 pF and  $C_{\rm M}$  = 10 pF. Determine the series and parallel resonant frequencies of the crystal.

### Solution

- 1. Series resonant frequency,  $f_S = 1/2\pi\sqrt{LC_S} = 1/(6.283\sqrt{2.5 \times 0.01 \times 10^{-12}})$ = 1.006614 MHz.

- 2. Equivalent capacitance  $C_{\rm p}$  for the parallel resonant circuit  $C_{\rm p} = 0.01 \times 10^{-12} \times 10 \times 10^{-12} / (0.01 \times 10^{-12} + 10 \times 10^{-12}) \ {\rm pF} = 0.00999 \ {\rm pF}$ 3. Parallel resonant frequency,  $f_{\rm p} = 1/2\pi \sqrt{LC_{\rm p}}$ .

4. Substituting the values, we get  $f_{\rm p} = 1/(6.283 \sqrt{2.5 \times 0.00999 \times 10^{-12}}) = 1.007117 \ {\rm MJ}$

# 12.16 Voltage-Controlled Oscillators

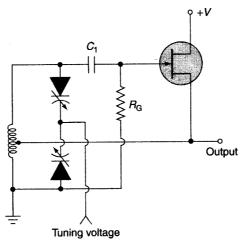

voltage-controlled oscillator (VCO) is an oscillator circuit in which the frequency of oscillations can be  $m{\Lambda}$ varied by an applied DC control voltage. This is achieved by having a voltage-dependent capacitor commonly known as varicap or a varactor diode as a part of the frequency-determining tank circuit.

Hartley and Clapp oscillator configurations are particularly suited to building VCOs as in both cases, the frequency-determining LC circuit has a single capacitor and tuning can be easily done by replacing this capacitor by a varactor diode. Figure 12.43 shows the basic voltage-controlled Hartley oscillator configured around a junction FET. A similar circuit could be configured around a bipolar transistor also. In the circuit shown in Figure 12.43, the amplifier is configured as common-drain amplifier with voltage gain slightly less than unity. In this case, the feedback factor is greater than one as the output signal appears across portion of the coil between source terminal and ground and the feedback signal appears across the whole of the coil winding.

Use of a single varactor diode is usually discouraged. This is because of the reason that for small values of DC control voltages, the varactor diode may start conducting at either of the peaks of the RF signal depending upon how it is connected in the circuit. Conducting diode reduces the Q-factor of the tank circuit and deteriorates the phase noise performance. Back-to-back connection of two varactor diodes overcomes this problem.

Figure 12.43 Voltage-controlled Hartley oscillator.

Another application of VCO is in fine tuning of crystal oscillators. The oscillator frequency may be varied by few tens of parts per million as the high value of Q-factor in the case of crystals allows pulling only over a small range. Fine tuning of crystal oscillator frequency may be needed to adjust output frequency to either match or be an exact multiple of some external reference. Voltage-controlled fine tuning of crystal oscillators may also be employed in temperature-compensated VCOs (TCVCXO) to correct the temperature dependence of oscillator frequency.

# 12.17 Frequency Stability

$\Gamma$  requency stability of an oscillator is a measure of its ability to maintain a constant oscillation frequency for as long a time period as possible. The oscillation frequency depends upon a large number of circuit features, which include circuit components, stray elements, supply voltages, characteristic parameters of active devices and so on. While one could pay due attention to choice of circuit components, use of clean and regulated supply voltages, etc., it may not be practical to identify location and estimation of magnitude of stray capacitances and inductances. This implies that it would be extremely hard to take remedial measures to counter the frequency drift caused by these elements. Equally impractical would be neutralizing the ill effects of instability of characteristic parameters of active devices.

Fortunately though, not all circuit features influence the oscillation frequency to the same extent. Oscillation frequency is usually far more sensitive to variation in a small number of circuit features than it is to the large number of remaining circuit features. For example, in the case of RC phase shift and Wien bridge oscillator circuits, frequency stability is largely dependent upon stability of R and C. Similarly, in an LC oscillator, it would mainly depend upon stability of L and C.

## Frequency Stability Criterion

According to the frequency stability criterion, if there exists a small set of elements which introduces a large phase change (d $\theta$ ) for a given change in frequency (d $\omega$ ), then higher the value of d $\theta$ /d $\omega$ , more will be the dependence of  $\omega$  on this set of elements as compared to its dependence on other circuit features. In the limit when  $d\theta/d\omega$  approaches infinity;  $\omega$  becomes independent of all other features and depends only on this small set of elements.

It can also be argued that  $d\theta/d\omega$  is a measure of frequency stability of the oscillator and a higher value of  $d\theta/d\omega$  means higher frequency stability. The argument goes as follows. Let us assume that one of the circuit features other than one of the elements of the small set mentioned above undergoes a variation. As a consequence of this variation, if the loop phase shift criterion were earlier satisfied at the operational frequency, it would no longer be satisfied after the variation takes place. The operational frequency must therefore shift in order to restore the loop phase shift back to zero. But if there were a small set of elements which at the nominal oscillation frequency produced a large change in phase for a given change in frequency, then the required frequency change to restore the loop phase shift condition would also be very small. This, in other words, means that the oscillator exhibits a high level of frequency stability.

This concept can be used to explain relatively higher frequency stability of LC oscillators in general, which improves with increase in the value of the Q-factor of the LC resonant circuit. It can similarly be used to explain the exceptionally high-frequency stability of crystal oscillators. In the case of LC oscillators, the reactance changes from capacitive to inductive around the frequency of resonance. Higher the Q-factor of the LC circuit, more abrupt is this change of phase. This further implies that higher Q-factor leads to a higher  $d\theta/d\omega$  and consequently higher frequency stability. The frequency stability can be quantified by computing the magnitude of  $d\theta/d\omega$  at the nominal oscillation frequency by differentiating the expression for the phase angle for the transfer function of the feedback network with respect to  $\omega$ .

#### **EXAMPLE 12.16**

Derive the relevant expression to prove that the Wien bridge oscillator exhibits better frequency stability at relatively lower oscillation frequencies and that the frequency stability deteriorates with increase in oscillation frequency.

#### Solution

- 1. The expression for phase angle  $(\theta)$  as a function of frequency  $(\omega)$  in the case of Wien bridge oscillator can be written as  $\theta = 90^{\circ} - \tan^{-1}[3 \omega RC/(1 - \omega^2 R^2 C^2)]$ . This equation is obtained by substituting  $R_1 = R_2 = R$  and  $C_1 = C_2 = C$  in Eq. (12.36).

- 2. The above equation can also be written as  $\theta = \tan^{-1}[(1 \omega^2 R^2 C^2)/3\omega RC]$ .

- 3. In general (d/dx)  $(tan^{-1}u) = [1/(1+u^2)] \times du/dx$ .

- **4.** Using this formula,  $d\theta/d\omega = KRC$ , where K is a constant.

- 5. The above expression implies that product RC needs to have a higher value in order to have higher  $d\theta/d\omega$  and therefore higher stability.

- 6. Higher RC means lower operating frequency.

- 7. This proves that the Wien bridge oscillator exhibits better frequency stability at lower oscillation frequencies and that the frequency stability deteriorates as the frequency of oscillation increases.

### **KEY TERMS**

Armstrong oscillator Barkhausen criterion Bubba oscillator

Buffered RC phase shift oscillator Clapp oscillator

Colpitt oscillator Crystal oscillator Frequency stability Hartley oscillator LC oscillators Meissner oscillator Pierce oscillator Quadrature oscillator RC oscillators RC phase shift oscillator Series-fed LC oscillator Shunt-fed LC oscillator Tickler coil Tickler oscillator Twin-T oscillator Wien bridge oscillator Voltage-controlled oscillator

# **OBJECTIVE-TYPE EXERCISES**

## **Multiple-Choice Questions**

- 1. According to Barkhausen criterion for sustained oscillations,

- **a.**  $\beta A < 1$ .

- **b.**  $\beta A > 1$ .

- c.  $\beta A = 1$ .

- **d.**  $\beta A = 0$ .

- 2. The condition that decides the oscillator's output frequency is

- a. loop gain should at least be unity.

- **b.** loop phase shift should be zero or integral multiple of  $2\pi$  radians.

- c. loop gain should be precisely unity.

- d. loop phase shift should be precisely zero radian.

- 3. In a conventional transistor RC phase shift oscillator using lead-type feedback network, frequency of oscillations is given by

$$\mathbf{a.} \quad f = \frac{1}{2\pi RC}$$

$$b. f = \frac{1}{2\pi\sqrt{RC}}$$

$$c. \quad f = \frac{1}{2\pi\sqrt{6}RC}$$

$$\mathbf{d.} \quad f = \frac{1}{2\pi\sqrt{3}RC}$$

**4.** In a Wien bridge oscillator, frequency of oscillations is given by

$$a. \quad f = \frac{3}{2\pi RC}$$

**b.**

$$f = \frac{1}{RC}$$

$$c. \quad f = \frac{1}{2\pi\sqrt{6}RC}$$

$$\mathbf{d.} \quad f = \frac{1}{2\pi\sqrt{3}RC}$$

- 5. Most popular oscillator configuration for audio applications is

- a. Hartley oscillator.

- b. Colpitt oscillator.

- c. Wien bridge oscillator.

- d. RC phase shift oscillator.

- **6.** Which of the following oscillator types provides extremely stable output frequency?

- a. Hartley oscillator.

- **b.** Wien bridge oscillator.

- c. Crystal oscillator.

- d. Clapp oscillator.

- 7. Pick the odd-one out.

- a. Hartley oscillator.

- **b.** Colpitt oscillator.

- c. Clapp oscillator.

- d. Wien bridge oscillator.

- **8.** Of the following, the oscillator with the most stable oscillation frequency is

- a. Clapp oscillator.

- b. Colpitt oscillator.

- c. Hartley oscillator.

- d. Armstrong oscillator.

- **9.** The series and parallel resonant frequencies of a quartz crystal are

- a. the same.

- b. spaced far apart.

- c. very close to each other.

- **d.** in the range of tens of MHz.

- **10.** The feedback network of a conventional RC phase shift oscillator uses

- a. three lag-type RC sections.

- b. three lead-type RC sections.

- three RC sections of either lead or lag type.

- d. twin-T notch filter.

- 11. In the case of a buffered RC phase shift RC oscillator, the required minimum value of amplifier gain is

- **a.** 29.

- **b.** 8.

- **c.** 3.

- **d.** 16.

- 12. According to the frequency stability criterion,

- higher  $|d\theta/d\omega|$  means higher frequency stability.

- **b.** higher  $|d\theta/d\omega|$  means lower frequency stability.

- frequency stability is independent of  $|d\theta/d\omega|$ .

- d. higher value of Q-factor means lower frequency stability.

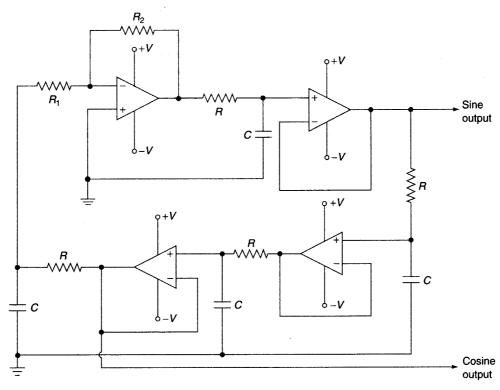

# Identify the Oscillator Configuration

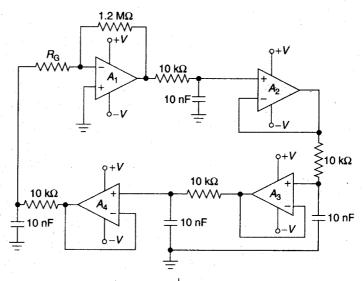

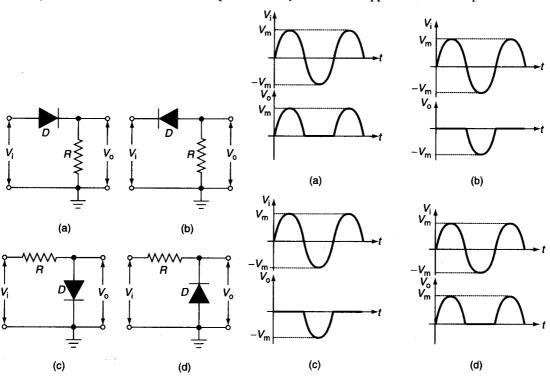

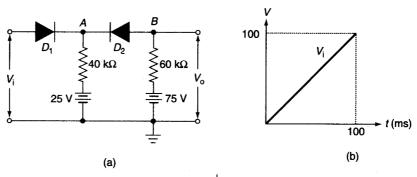

Identify the oscillator circuits of Figure 12.44. Choose from Hartley oscillator, Colpitt oscillator, Clapp oscillator, Tickler oscillator, Pierce oscillator, Wien bridge oscillator, RC phase shift oscillator, Crystal oscillator, Bubba oscillator and Twin-T oscillator.

Figure 12.44 | Identify the oscillator configuration.

Figure 12.44 | Continued.

# **REVIEW QUESTIONS**

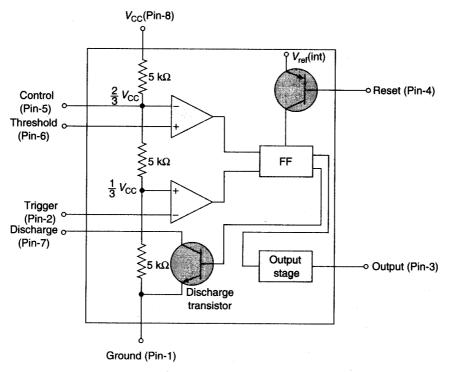

- 1. How does the circuit configuration of an oscillator differ from that of an amplifier? What are the different constituents of an oscillator circuit?